| Vocademy |

Part 8: Operations and Ports

Input and Output

Input and output (I/O) devices are wired into the computer so that when the CPU connects to specific memory addresses, it connects to an input or output device. If the computer uses memory-mapped I/O, the memory and I/O devices share the same memory space. The CPU will find memory at most memory addresses, but at a few other addresses, it will connect to an I/O device. If the computer uses port-mapped I/O, the CPU will disconnect from memory and connect to the I/O subsystem to perform input and output. However, the same address and data buses communicate with memory and I/O devices.

The I/O Address

Since each I/O device is found at a particular memory address, the device must be configured to appear at a specific address (or range of addresses). The computer must know the address to connect to a particular device. Therefore, every I/O device must have an I/O address. Today, these parameters are configured by the plug-and-play system. However, before Windows 95 (at one time, the only operating system that could use plug and play), computer technicians had to keep track of what devices were using what I/O addresses and then configure all devices and drivers to communicate with each other. This goes for the other parameters listed below, too. Technicians had to carefully configure I/O addresses, IRQs, DMA channels, and ROM addresses so that no two devices tried to use the same resources.

Interrupts

An interrupt is a sequence where the CPU stops what it is doing and executes a different program (once finished with the new program, it will return to what it was doing). Interrupts are not something a user is ever aware of. For example, an interrupt is executed every time you press a key on the keyboard or click a mouse button. Moving the mouse generates several interrupts per second.

Not all devices use interrupts; only input devices that need to tell the CPU when they have data ready. The original printer port did not use interrupts, and neither do serial printers.

There are three types of interrupts: non-maskable interrupts, maskable interrupts (interrupt request), and software interrupts. The CPU reset function can be considered an interrupt but is handled differently.

Non-maskable interrupt (NMI)

On the original IBM PC, a parity error generated the only documented NMI. This would display "PARITY ERROR" and halt the processor. Some later PC clones would use the NMI pin to trigger translation software if a program tried to access hardware incompatible with an IBM PC. Otherwise, NMIs are not an essential part of the PC architecture.

Interrupt request (IRQ)

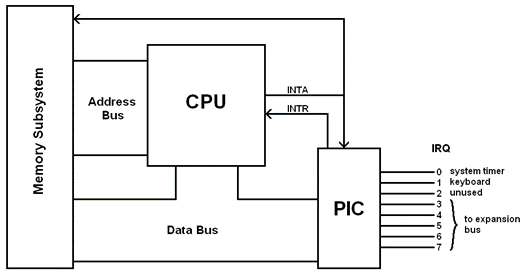

On the original IBM PC, there was a single Programmable Interrupt Controller (PIC). This provided eight hardware input wires, called interrupt request lines (IRQs), numbered 0 through 7.

|

|

|

IRQ 0 connected to the system timer, IRQ 1 connected to the keyboard controller, and IRQ 2 was unused (reserved for a video display that was never implemented). IRQs 3 through 7 went to the expansion bus, so they were available to plug in I/O cards. Each I/O card that used an IRQ had to be configured to use an IRQ that was not used by any other device.

The basic sequence of an IRQ is as follows:

- The PIC gets a logical high signal on one of the IRQ wires (the PIC handles the IRQ priority; lower numbers have higher priority).

- When a particular IRQ's turn comes up, the PIC puts a logical high on the CPU's INTR pin.

- The CPU will finish the instruction it is currently working on and then push the contents of the program counter to the stack (this stores the CPU's current location in memory so that it can return to what it was doing when it is finished dealing with the interrupt).

- The CPU sends two logical high pulses to the INTA (interrupt acknowledge) wire. The INTA wire connects to the memory subsystem as well as the PIC. The memory subsystem disconnects from the data bus so that the PIC can connect to it.

- The PIC puts a byte on the data bus. This byte will be the number 0 through 7 (00000000 - 00000111), depending on which IRQ is being serviced.

- The CPU takes the byte from the PIC and multiplies it by 4 (shifts the data left by two bits).

- The CPU uses the

result of the previous operations as a pointer to the interrupt vector lookup

table.

- The interrupt vector lookup table is at the beginning of memory. It is organized into four-byte blocks, where each block holds the address of an interrupted service routine. Therefore, the fourth block, which starts at the 12th byte of memory, holds the address of the interrupt service routine for IRQ 3 (numbering starts at 0, so the 4th IRQ is number 3).

- The CPU jumps to the address specified in the table and runs whatever program is found there. When the CPU encounters an IRET instruction (return from interrupt), it pulls the original program counter value off the stack. This puts the CPU back where it was when it received the interrupt request.

This is a short and to-the-point description of the IRQ sequence, i.e., the CPU stops what it is doing, runs some other program until it reaches an IRET instruction, then goes back to what it was doing. The "some other program" will be the interrupt service routine that handles input and output for a particular device. For example, when you press a key on the keyboard, a signal is sent to IRQ 1. The computer stops what it is doing and ultimately jumps to the interrupt service routine for the keyboard. This will cause the CPU to do whatever it does to connect to the keyboard controller, get the two bytes that hold the key code, and put that in the key buffer. The CPU then returns to whatever program it was running when it received the IRQ.

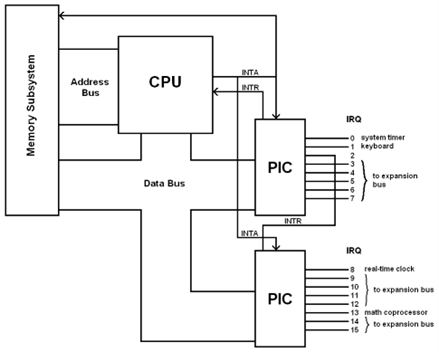

The PIC in the IBM PC is designed to have a main PIC with up to eight secondary PICs connected to it. Each secondary PIC connects its INTR wire to one of the IRQ wires of the main PIC. With such an arrangement, you can have up to 64 IRQs. The IBM PC-AT added a second PIC. The INTR wire from the second PIC is connected to IRQ 2 or the first PIC.

|

|

|

With two PICs, the AT

could handle 15 IRQs from I/O devices. IRQ 2 was used for the second PIC. Since

IRQs 8 through 15 are ultimately cascaded through IRQ 2, they have higher

priorities than IRQs 3 through 7.

In the days when it was important to keep

track of IRQs, it was said that IRQ 9 was cascaded to IRQ 2 and that IRQ 9 and

IRQ 2 were treated as the same IRQ. However, IRQs 8 through 15 are cascaded

through IRQ2. I have been unable to find official documentation that IRQ 9 had

special treatment.

Software interrupt

A software interrupt is an interrupt instruction. It is not like a normal interrupt where the computer stops in the middle of a program to do something unrelated, but is a convenient way to perform repetitive functions like input and output.

Software interrupts use the same interrupt vector lookup table as IRQs. A software interrupt is generated with the INT instruction followed by an interrupt number. For example, the assembly language instruction "INT 13h" causes the CPU to look up the 20th interrupt vector (13 in hexadecimal is 19 in decimal, the 20th number counting from zero) and jump to the address it finds there. In particular, the CPU will multiply the hexadecimal number 13 by 4, resulting in hexadecimal 4C, and use this as a pointer to the 20th four-byte block in the interrupt vector lookup table. Then, it uses the numbers stored there to assemble the address of the disk's interrupt service routine and jumps there.

Below is an example of input and output with software interrupts. This is how you would read a group of sectors from a disk drive (hard disk or floppy disk). The actual commands are not shown (except for the INT command) because this is not a tutorial in programming for the IBM PC, just an overview of how I/O works. Each step below would be a few instructions that do what is described. Once the proper internal registers of the CPU are loaded with the relevant information, the INT instruction is executed.

Example of steps to read sectors from a disk drive:

o Put the number 02 in the high half

of the A register (tells the routine you want to read sectors).

o Put the

number of sectors to read in the low half of the A register (up to 256 sectors)

o Put the starting track in the high half of the C register

o Put the

starting sector in the low half of the C register

o Put the disk side number

in the high half of the D register

o Put the drive number in the low half of

the D register

o Put the address where you want the data to be stored in the

ES and BS registers

o Execute the INT 13h instruction

After the above program is executed, the data will be retrieved from the specified sectors and put in the specified memory block.

Direct memory access

Normally, an input operation requires the CPU to switch to input mode, get a byte from a device, switch to memory mode, and put the byte into RAM. This is repeated over and over, byte after byte, until the entire operation is finished. This is not exactly efficient.

The PC has a direct memory access (DMA) subsystem. A few I/O devices can use this system to send data directly to memory, bypassing the CPU. The DMA is managed by two DMA controllers that each handle four DMA channels. One DMA controller is cascaded into a channel of the other so that seven channels are available to I/O devices. Like other I/O resources, the main thing to remember is that no two devices can use the same DMA channel. Some DMA devices are floppy disks, sound cards (sometimes two channels), and later parallel ports.

DMA, as described above, is not used by very many devices. However, you may hear of other types of DMA, such as ultra DMA (UDMA) and bus mastering devices. ATA hard disks use UDMA, and some other devices are bus mastering. A bus-mastering device can communicate directly with the memory subsystem and other bus-mastering devices after signaling the CPU to disconnect from the address/data bus.

ROM addresses

A few I/O devices have BIOS extension software in ROM. During the POST, the computer will search the memory between 640 k and the BIOS for such ROM programs. When found, control is turned over to the ROM, which initializes the device before returning control to the main BIOS. Naturally, devices that have ROM BIOS extensions must be configured so that no two devices appear in the same memory address range.

All video cards have a ROM BIOS extension. SCSI host adapters may have them, but not always. Most Ethernet adapters have a socket for a boot ROM, making it possible to boot over a network. Few plug-in Ethernet adapters have this boot ROM, but most motherboards with built-in Ethernet have such boot ROMs.

Plug and Play

Until 1995, technicians had to carefully track what resources were being used by what devices. Devices needed to be configured to use non-conflicting resources, and the drivers had to be configured to use the correct resources to access a particular device. Memorizing lists of common devices and the resources they used was a necessary part of the technician's job.

In the mid-1990s, Plug and Play was developed. This eliminated technician intervention in configuring I/O devices and the resource conflicts that resulted from mistakes. Dealing with I/O addresses, IRQs, DMA channels, and ROM addresses is virtually a thing of the past with PCs. However, you may still encounter resource configuration with other computerized systems.

If you look at the device manager to see what resources are being used, you may see multiple devices using the same resources. This would have been heresy 25 years ago (more like a total disaster), but with virtualized resources, they can now be shared with modern operating systems.

Myth:

The IBM PC uses non-maskable interrupts (NMIs) for serious or fatal errors.

Non-maskable

interrupts are used for time-critical operations. For example, the Atari 8-bit

computers used NMIs for video processing. Early IBM-compatible computers used an

NMI when a memory parity error was detected, but today's PCs don't use

non-maskable interrupts.

| Vocademy |