| Vocademy |

Registers

Digital counters and frequency dividers

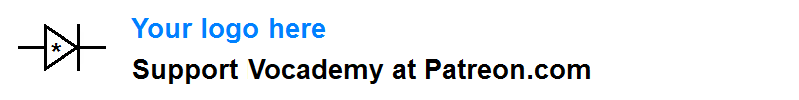

Divide-by-two frequency divider

A J-K flip-flop that is set to toggle on each clock change acts as a frequency divider. Each time the clock input goes from high to low the Q output toggles (flips its state from 0 to 1 or vice versa). If the clock input is presented with a steady stream of pulses at a regular frequency, the Q output produces a square wave with a frequency of ½ the clock frequency.

|

|

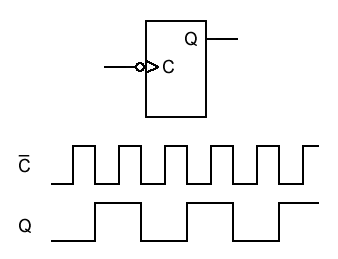

A toggling

flip-flop is also a divide-by-two frequency divider. The Q output will

produce a square wave that is ½ the frequency of the clock input. If you take the above flip-flop and connect the Q output to the clock input of another toggling flip-flop, you get a second frequency divider that works on the output of the first. The result is a circuit that divides the original input frequency by 4. |

|

|

|

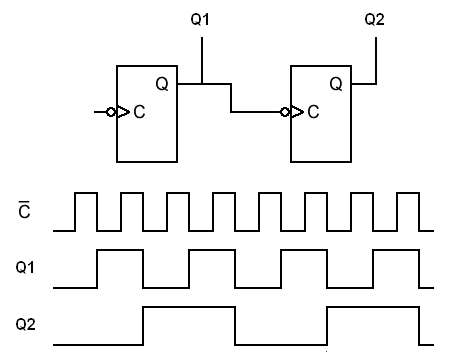

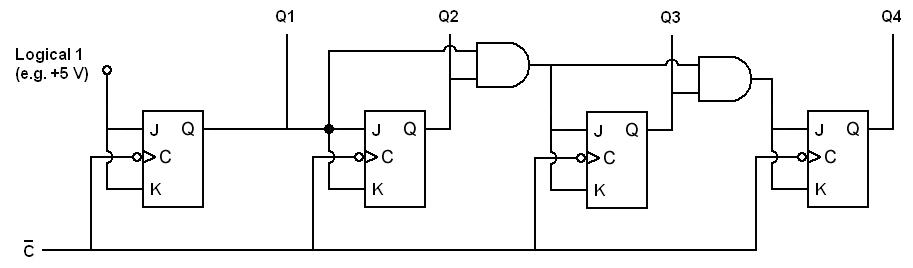

Asynchronous Binary Counter

If you continue in the same manner, each flip-flop divides the output of the previous flip-flop by 2. The following circuit uses four toggling flip-flops to create a divide-by-16 circuit.

|

| An asynchronous divide-by-16 counter |

These circuits are called counters because the Q outputs present a binary number equal to the number of clock pulses presented to the first clock input over time. As shown below, the last flip-flop has the most significant bit (MSB) of the counter.

|

| The Q outputs of a binary counter. The C column shows the number of clock pulses. The other columns show the Q outputs. Notice that the binary number presented by the group of outputs corresponds to the number of clock pulses. After 15 pulses the output recycles to all zeros and the count starts over. |

This circuit is called an asynchronous counter because the outputs don't all change at the same time. There is a short delay (propagation delay) between each flip-flop because it takes time for each flip-flop to react to its clock input.

Synchronous binary up counter

The following circuit is a synchronous binary counter. The difference between this counter and the asynchronous counter is that all the flip-flops are clocked at the same time. Therefore, they all changed at the same time. This design sets up the J and K inputs such that the outputs change as required to present a count of clock pulses on the outputs.

|

|

|

Other counters

A counter similar to the synchronous counter above can be made such that the J and K inputs are set up where counter transitions directly from 1001 (decimal 9) to 0000 (decimal 0). This counter counts from 0 to 9 then back to 0, making a decimal counter (also called a decade counter, divide-by-10 counter or modulo 10 counter). This design is not shown here because it is not something an engineer would design and build but something you would buy as an integrated circuit.

In addition to binary and decade counters, you can find integrated circuit counters that count to 6 and 12. There are also counters that can be set to divide by any number as needed (called a modulo N counter or divide by N counter). The 4018 CMOS divide by N counter is a typical example that is manufactured by several companies.

Shift registers

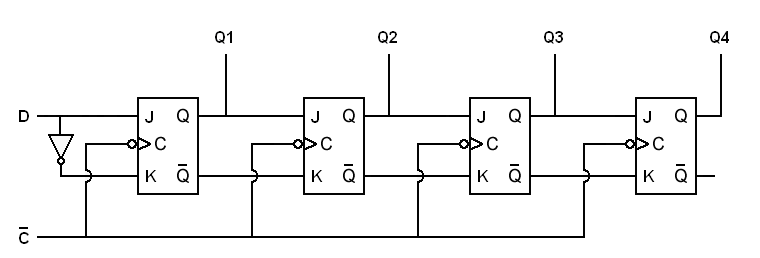

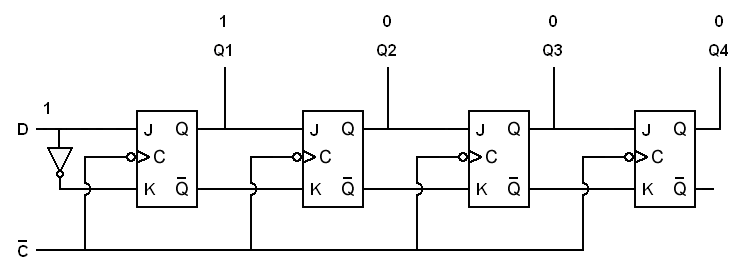

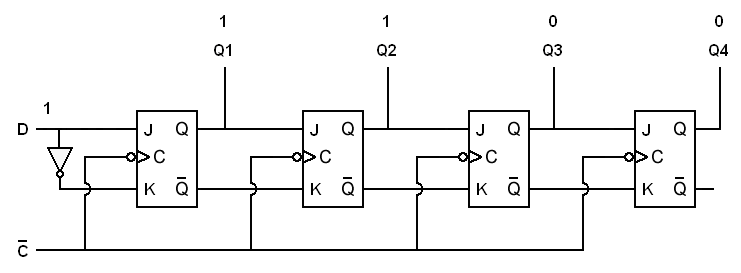

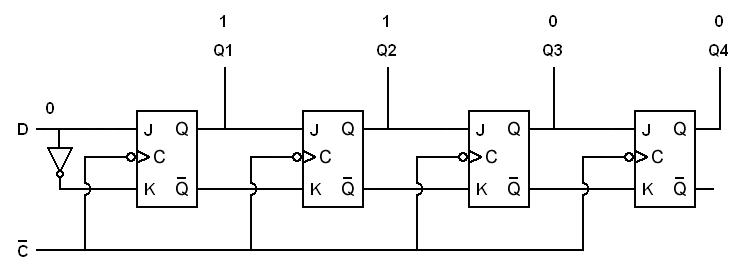

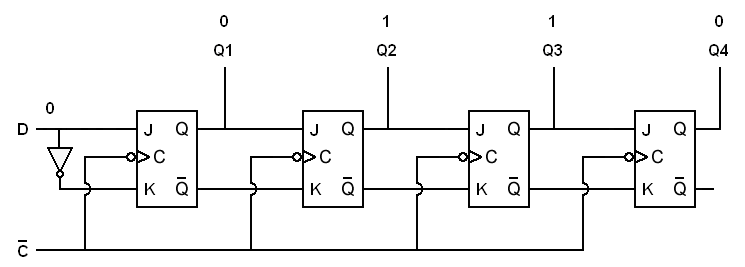

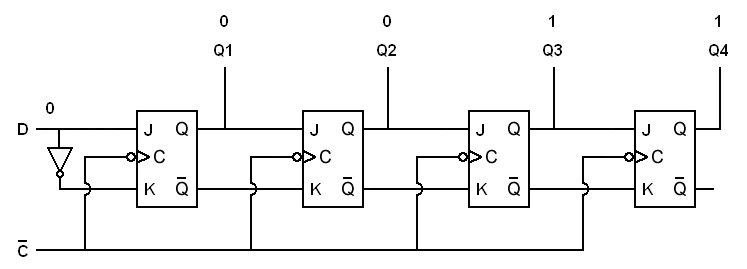

A shift register is a group of flip-flops that move all bits right or left on each clock pulse. The following circuit is one design for a shift register.

|

|

|

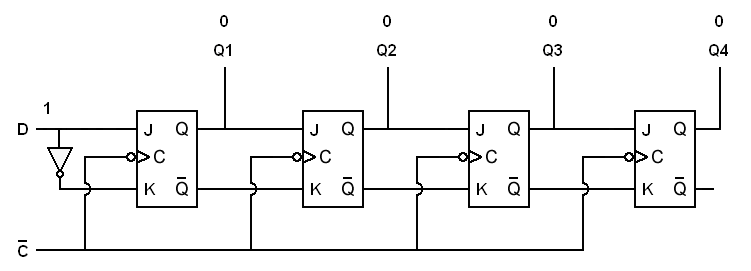

Notice that if D is made a logical 1 the J input of the first flip-flop is a 1 and the K is a 0. This causes the flip-flop to change its Q output to 1 when a clock pulse arrives. Now the J input of the second flip-flop is 1 and the K of the second flip-flop is 0. On the next clock pulse, its Q output goes high. On every clock pulse, the data on each flip-flop transfers to the next flip-flop to the right. New data can be inserted into the data train through the D input at any time.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Shift registers are often used to convert serial data to parallel data and vice versa. Bits enter the register one at a time through the D input and shift down the register like a bucket brigade. In the example above, four bits can be shifted-in, one at a time (serial data). After that, the bits are available as a single group at the four Q outputs (parallel data). There are also shift registers that can be preset with parallel data which is then shifted out the rightmost flip-flop as serial data. Used in this manner a shifter register is called a serial-to-parallel or parallel-to-serial converter.

Some examples of shift

register circuits are the 4021, an 8-stage shift register, the 4031, a 64-stage

shift register and the 4035, a 4-stage shift register with parallel preset

inputs.

Julian's Logic: The 74HC595 Shift Register

| Vocademy |